Arm Solutions at Lightspeed

#### How (not) to write PCI(e) controller drivers in Linux Kernel

Manivannan Sadhasivam - Linaro

# Why this talk?

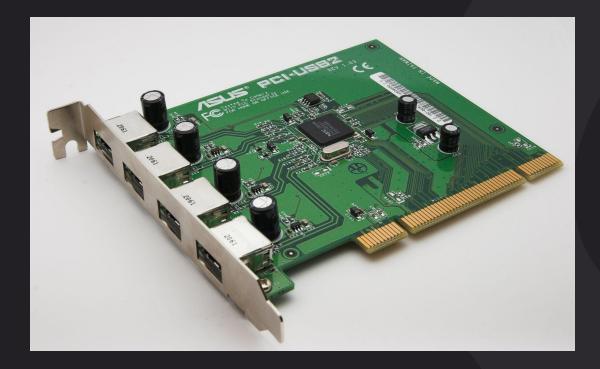

Peripheral Component Interconnect

**PCI Express**

PCI

- Peripheral Component Interconnect

- PCIe PCI Express (Software compatible with PCI)

**PCI Express**

PCI

- Peripheral Component Interconnect

- PCIe PCI Express (Software compatible with PCI)

- High speed expansion bus for PCs, Servers, Laptops, Mobiles

- Marketed as Plug and Play (Hotplug)

**PCI Express**

PCI

- Peripheral Component Interconnect

- PCIe PCI Express (Software compatible with PCI)

- High speed expansion bus for PCs, Servers, Laptops, Mobiles

- Marketed as Plug and Play (Hotplug)

- Specification developed by Intel

- Later moved under PCI-SIG

**PCI Express**

PCI

- Peripheral Component Interconnect

- PCIe PCI Express (Software compatible with PCI)

- High speed expansion bus for PCs, Servers, Laptops, Mobiles

- Marketed as Plug and Play (Hotplug)

- Specification developed by Intel

- Later moved under PCI-SIG

- Works in Lanes (Tx/Rx differential pairs)

**PCI Express**

PCI

- Peripheral Component Interconnect

- PCIe PCI Express (Software compatible with PCI)

- High speed expansion bus for PCs, Servers, Laptops, Mobiles

- Marketed as Plug and Play (Hotplug)

- Specification developed by Intel

- Later moved under PCI-SIG

- Works in Lanes (Tx/Rx differential pairs)

- Supports Power Management (PCI PM, ASPM)

**PCI Express**

PCI

- Peripheral Component Interconnect

- PCIe PCI Express (Software compatible with PCI)

- High speed expansion bus for PCs, Servers, Laptops, Mobiles

- Marketed as Plug and Play (Hotplug)

- Specification developed by Intel

- Later moved under PCI-SIG

- Works in Lanes (Tx/Rx differential pairs)

- Supports Power Management (PCI PM, ASPM)

- Supports I/O Virtualization (SR-IOV)

**PCI Express**

PCI

#### PCle Architecture

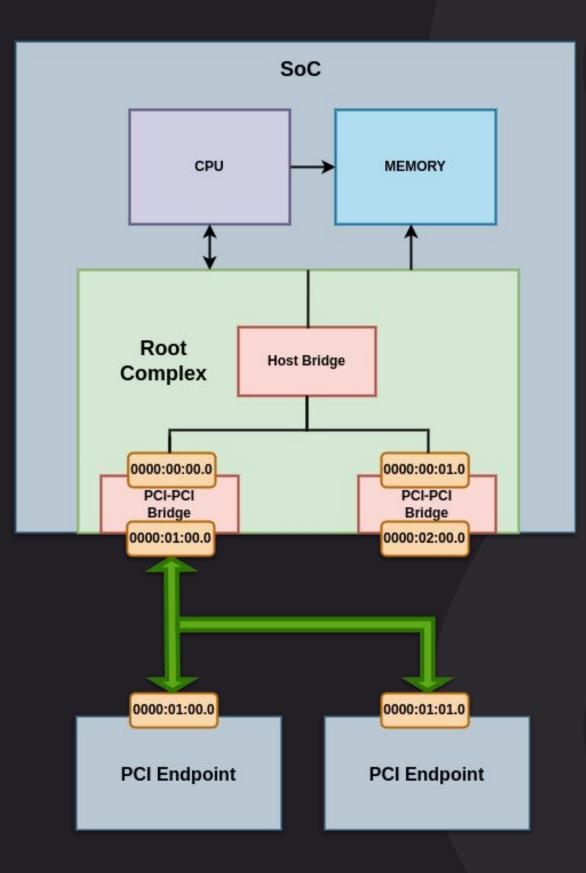

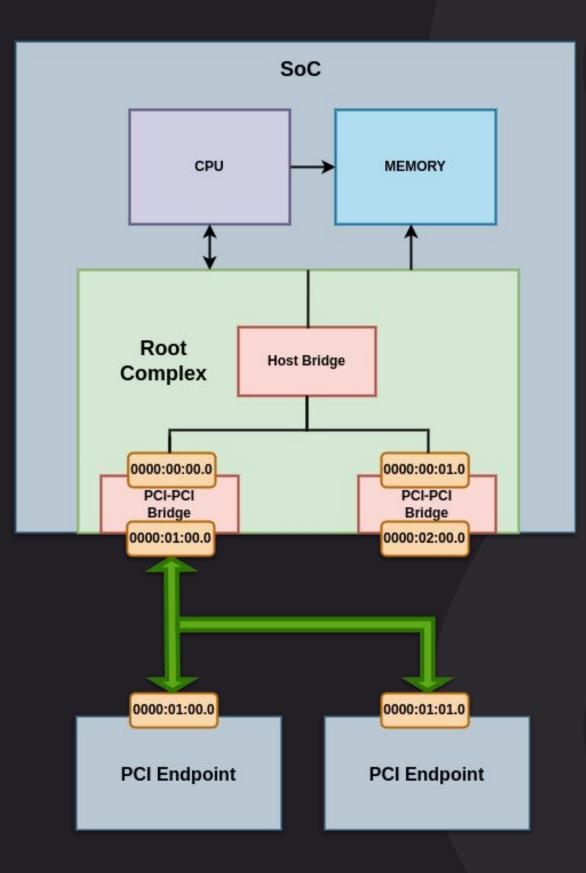

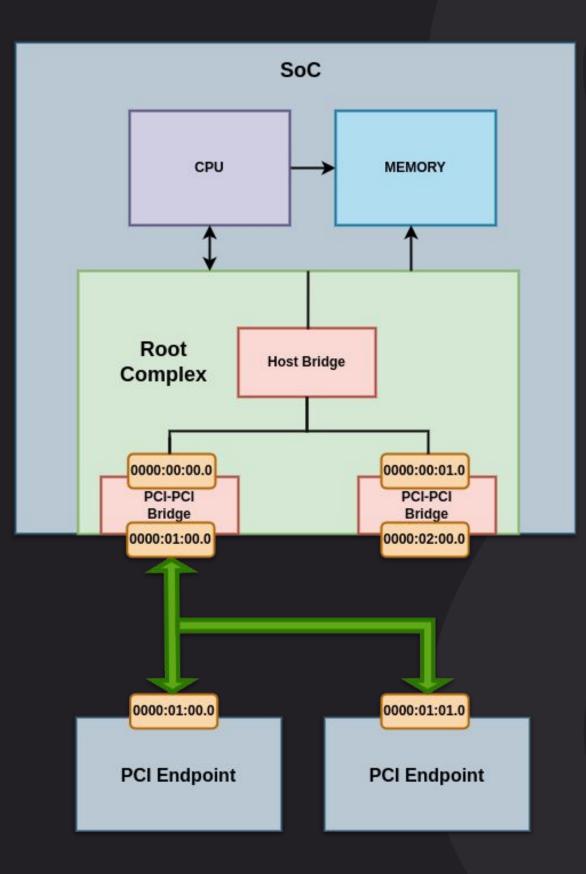

#### PCIe Architecture

- Point to Point topology

- PCIe Root Complex Host

- PCle Endpoint Device

#### PCIe Architecture

- Point to Point topology

- PCIe Root Complex Host

- PCle Endpoint Device

- Each PCIe device is identified by Bus Device

Function (BDF) identifier

- 8 bit Bus 256 Busses

- 5 bit Device 32 Devices

- 3 bit Function 8 Functions

#### PCIe Architecture

- Point to Point topology

- PCIe Root Complex Host

- PCle Endpoint Device

- Each PCIe device is identified by Bus Device

Function (BDF) identifier

- 8 bit Bus 256 Busses

- 5 bit Device 32 Devices

- 3 bit Function 8 Functions

- PCIe Switches are often used for port expansion

• Linux kernel supported PCI from early v1.3 release and PCIe since v2.6

- Linux kernel supported PCI from early v1.3 release and PCIe since v2.6

- Code organization:

- Linux kernel supported PCI from early v1.3 release and PCIe since v2.6

- Code organization:

- PCI Core drivers drivers/pci/

- Linux kernel supported PCI from early v1.3 release and PCIe since v2.6

- Code organization:

- PCI Core drivers drivers/pci/

- PCIe Feature drivers drivers/pci/pcie/

- Linux kernel supported PCI from early v1.3 release and PCIe since v2.6

- Code organization:

- PCI Core drivers drivers/pci/

- PCIe Feature drivers drivers/pci/pcie/

- PCI Controller drivers drivers/pci/controllers/

- Linux kernel supported PCI from early v1.3 release and PCIe since v2.6

- Code organization:

- PCI Core drivers drivers/pci/

- PCIe Feature drivers drivers/pci/pcie/

- PCI Controller drivers drivers/pci/controllers/

- PCI Endpoint core drivers/pci/endpoint/

- Linux kernel supported PCI from early v1.3 release and PCIe since v2.6

- Code organization:

- PCI Core drivers drivers/pci/

- PCIe Feature drivers drivers/pci/pcie/

- PCI Controller drivers drivers/pci/controllers/

- PCI Endpoint core drivers/pci/endpoint/

- PCI Client drivers All over the place (Ethernet, WLAN, NVMe etc...)

- Linux kernel supported PCI from early v1.3 release and PCIe since v2.6

- Code organization:

- PCI Core drivers drivers/pci/

- PCIe Feature drivers drivers/pci/pcie/

- PCI Controller drivers drivers/pci/controllers/

- PCI Endpoint core drivers/pci/endpoint/

- PCI Client drivers All over the place (Ethernet, WLAN, NVMe etc...)

• What they do?

- What they do?

- Initialize resources (clocks, regulators, PHY, power domain etc...)

- devm\_pci\_alloc\_host\_bridge()

- What they do?

- Initialize resources (clocks, regulators, PHY, power domain etc...)

- devm\_pci\_alloc\_host\_bridge()

- Setup Root Port(s)

- What they do?

- Initialize resources (clocks, regulators, PHY, power domain etc...)

- devm\_pci\_alloc\_host\_bridge()

- Setup Root Port(s)

- Setup MSI/MSI-X/INTx

- What they do?

- Initialize resources (clocks, regulators, PHY, power domain etc...)

- devm\_pci\_alloc\_host\_bridge()

- Setup Root Port(s)

- Setup MSI/MSI-X/INTx

- Setup Address Translation Unit (ATU) for MEM/IO region

- What they do?

- Initialize resources (clocks, regulators, PHY, power domain etc...)

- devm\_pci\_alloc\_host\_bridge()

- Setup Root Port(s)

- Setup MSI/MSI-X/INTx

- Setup Address Translation Unit (ATU) for MEM/IO region

- Setup DMA

- What they do?

- Initialize resources (clocks, regulators, PHY, power domain etc...)

- devm\_pci\_alloc\_host\_bridge()

- Setup Root Port(s)

- Setup MSI/MSI-X/INTx

- Setup Address Translation Unit (ATU) for MEM/IO region

- Setup DMA

- Start LTSSM

- What they do?

- Initialize resources (clocks, regulators, PHY, power domain etc...)

- devm\_pci\_alloc\_host\_bridge()

- Setup Root Port(s)

- Setup MSI/MSI-X/INTx

- Setup Address Translation Unit (ATU) for MEM/IO region

- Setup DMA

- Start LTSSM

- Enumerate endpoint devices

- pci\_host\_probe()

∞linaro™

## 4 Common Mistakes & Solutions

CONTRACT PRANAMENTS

#### Mistake 1 Mistake 1

# Mistake 1

- Root ports not described in firmware

- Devicetree mostly

# Mistake 1

- Root ports not described in firmware

- Devicetree mostly

- Controller node ends up hosting root port properties

#### Mistakes and Solutions Mistake 1

| • | Root ports not described in firmware  |      |      |    |         |      |      | <pre>pcie0: pcie0600000 {     compatible =</pre> |   |

|---|---------------------------------------|------|------|----|---------|------|------|--------------------------------------------------|---|

|   | <ul> <li>Devicetree mostly</li> </ul> |      |      |    |         |      |      |                                                  |   |

| • | Controller                            | node | ends | up | hosting | root | port | []<br>iommu-map =                                | V |

|   | properties                            |      |      |    |         |      |      | []                                               | V |

```

"qcom,pcie-sm8250";

0x0 &apps_smmu 0x1c00 0x1>,

0x100 &apps smmu 0x1c01 0x1>;

phys = <&pciephy_0>;

phy-names = "pciephy";

[...]

```

[....]

};

reset-gpios = <&tlmm 79 GPI0\_ACTIVE\_LOW>; wake-gpios = <&tlmm 81 GPIO ACTIVE HIGH>;

• Move Root Port properties to Root Port

• Move Root Port properties to Root Port

pcie0: pcie@600000 {

[...]

pcieport0: pcie@0 {

ranges;

};

};

```

compatible = "qcom,pcie-sm8250";

device_type = "pci";

reg = <0x0 0x0 0x0 0x0 0x0>;

bus-range = <0x01 0xff>;

#address-cells = <3>;

#size-cells = <2>;

iommu-map = <0x0 & apps smmu 0x1c00 0x1>,

<0x100 &apps smmu 0x1c01 0x1>;

phys = <\&pciephy 0>;

phy-names = "pciephy";

reset-gpios = <&tlmm 79 GPI0 ACTIVE_LOW>;

wake-gpios = <&tlmm 81 GPIO ACTIVE HIGH>;

```

Slot/Endpoint power supplies defined in host bridge node

#### Mistakes and Solutions Mistake 2

• Slot/Endpoint power supplies defined in host bridge node

pcie0: pcie@600000 {

};

[...]

```

vpcie12v-supply = <&pcie0 12v>;

vpcie3v3-supply = <&pcie0 3p3v>;

vpcie3v3aux-supply = <&pcie0 3p3v aux>;

```

```

compatible = "qcom,pcie-sm8250";

```

• Define slot supplies in Root Port node

• Define slot supplies in Root Port node

pcie0: pcie@600000 {

[...]

[...]

};

```

compatible = "qcom,pcie-sm8250";

pcieport0: pcie@0 {

device_type = "pci";

reg = \langle 0 \times 0 \ 0 \times 0 \ 0 \times 0 \ 0 \times 0 \ 0 \times 0 \rangle;

bus-range = <0x01 0xff>;

```

```

vpcie12v-supply = <&pcie0 12v>;

vpcie3v3-supply = <&pcie0 3p3v>;

vpcie3v3aux-supply = <&pcie0 3p3v aux>;

```

- Define slot supplies in Root Port node

- Rely on PWRCTRL drivers (CONFIG\_PCI\_PWRCTL\*)

- Works for standard supplies

pcie0: pcie@600000 {

[...]

};

```

compatible = "qcom,pcie-sm8250";

pcieport0: pcie@0 {

device_type = "pci";

reg = \langle 0 \times 0 \ 0 \times 0 \ 0 \times 0 \ 0 \times 0 \ 0 \times 0 \rangle;

bus-range = <0x01 0xff>;

```

#### [...]

```

vpcie12v-supply = <&pcie0 12v>;

vpcie3v3-supply = <&pcie0 3p3v>;

vpcie3v3aux-supply = <&pcie0 3p3v aux>;

```

• Define Endpoint supplies in Endpoint node

• Define Endpoint supplies in Endpoint node

pcie0: pcie@600000 {

[...]

pcieport0: pcie@0 {

[...]

wifi@0 {

};

};

```

compatible = "qcom,pcie-sm8250";

device type = "pci";

reg = \langle 0 \times 0 \ 0 \times 0 \ 0 \times 0 \ 0 \times 0 \ 0 \times 0 \rangle;

bus-range = <0x01 0xff>;

compatible = "pcil7cb,1101";

reg = <0x10000 0x0 0x0 0x0 0x0;

vddrfacmn-supply = <&vreg pmu rfa cmn>;

vddaon-supply = <\&vreg pmu aon 0p59>;

vddwlcx-supply = <&vreg pmu wlcx 0p8>;

vddwlmx-supply = <&vreg pmu wlmx 0p85>;

vddrfa0p8-supply = <&vreg pmu rfa 0p8>;

vddrfa1p2-supply = <&vreg pmu rfa 1p2>;

vddrfa1p7-supply = <&vreg pmu rfa 1p7>;

vddpcie0p9-supply = <&vreg pmu pcie 0p9>;

vddpcie1p8-supply = <&vreg pmu pcie 1p8>;

```

- Define Endpoint supplies in Endpoint node • Rely on PWRSEQ drivers (CONFIG\_PCI\_PWRCTL\_PWRSEQ/CONFIG\_POWER\_ SEQUENCING\*)

- Works for complex supplies

pcie0: pcie@600000 {

[...]

pcieport0: pcie@0 {

[...]

wifi@0 {

};

};

```

compatible = "qcom,pcie-sm8250";

device type = "pci";

reg = \langle 0 \times 0 \ 0 \times 0 \ 0 \times 0 \ 0 \times 0 \ 0 \times 0 \rangle;

bus-range = <0x01 0xff>;

compatible = "pci17cb,1101";

reg = <0x10000 0x0 0x0 0x0 0x0>;

vddrfacmn-supply = <&vreg pmu rfa cmn>;

vddaon-supply = <\&vreg pmu aon 0p59>;

vddwlcx-supply = <&vreg pmu wlcx 0p8>;

vddwlmx-supply = <&vreg pmu wlmx 0p85>;

vddrfa0p8-supply = <&vreg pmu rfa 0p8>;

vddrfa1p2-supply = <&vreg pmu rfa 1p2>;

vddrfa1p7-supply = <&vreg pmu rfa 1p7>;

vddpcie0p9-supply = <&vreg pmu pcie 0p9>;

vddpcie1p8-supply = <&vreg pmu_pcie_1p8>;

```

#### Mistake 3 Mistake 3

• Mapping each Outbound translation using ATU

#### Mistakes and Solutions Mistake 3

• Mapping each Outbound translation using ATU

u32 busdev; [...]

```

unsigned int devfn, int where)

ret = dw pcie prog outbound atu(pci, &atu);

return NULL;

.map_bus = dw_pcie_other_conf_map_bus,

[...]

```

```

static void iomem *dw pcie other conf map bus(struct pci bus *bus,

struct dw pcie rp *pp = bus->sysdata;

struct dw pcie *pci = to dw pcie from pp(pp);

struct dw pcie ob atu cfg atu = \{0\};

int type, ret;

if (ret)

return pp->va cfg0 base + where;

static struct pci ops dw child pcie ops = {

```

[...]

}

};

{

#### **Mistakes and Solutions** Mistake 3

- Mapping each Outbound translation using ATU

- Inefficient and adds latency

int type, ret; u32 busdev; [...] if (ret) [...] [...]

{

}

};

```

static void iomem *dw pcie other conf map bus(struct pci bus *bus,

unsigned int devfn, int where)

struct dw pcie rp *pp = bus->sysdata;

struct dw pcie *pci = to dw pcie from pp(pp);

struct dw pcie ob atu cfg atu = \{0\};

ret = dw pcie prog outbound atu(pci, &atu);

return NULL;

return pp->va cfg0 base + where;

static struct pci ops dw child pcie ops = {

.map_bus = dw_pcie_other_conf_map_bus,

```

• Configure ECAM mode in bootloader

- Configure ECAM mode in bootloader

- Pros

- Ability to reuse existing controller drivers

- pci-host-generic.c

- Configure ECAM mode in bootloader

- Pros

- Ability to reuse existing controller drivers

- pci-host-generic.c

- Downside

- Requires firmware change

- Cannot reset the host bridge

- Configure ECAM mode in controller driver

- <u>Reference</u>

- Configure ECAM mode in controller driver

- <u>Reference</u>

- Pros

- Control lies with Linux Kernel

- Can reset the host bridge

- Configure ECAM mode in controller driver

- <u>Reference</u>

- Pros

- Control lies with Linux Kernel

- Can reset the host bridge

- Downside

- Requires a separate controller driver

#### Mistake 4 Mistake 4

<mark>63</mark>

• shutdown() callback often not defined

- shutdown() callback often not defined

- Developers get confused with remove()

- shutdown() callback often not defined

- Developers get confused with remove()

- Messes up endpoint state machine during warm reboot

• Define shutdown() callback

<mark>68</mark>

- Define shutdown() callback

- Put the endpoint into D3Cold

- Define shutdown() callback

- Put the endpoint into D3Cold

- Send PME\_Turn\_Off

- Define shutdown() callback

- Put the endpoint into D3Cold

- Send PME\_Turn\_Off

- Wait for PME\_TO\_Ack from endpoint

- Define shutdown() callback

- Put the endpoint into D3Cold

- Send PME\_Turn\_Off

- Wait for PME\_TO\_Ack from endpoint

- Assert PERST#

- Define shutdown() callback

- Put the endpoint into D3Cold

- Send PME\_Turn\_Off

- Wait for PME\_TO\_Ack from endpoint

- Assert PERST#

- Remove power

- Let the PWRCTRL driver take care of it!

### Thank you

<u>manivannan.sadhasivam@linaro.org</u> IRC: mani\_s